Xilinx FPGA控制器的Everspin STT-DDR4设计指南

2020-01-19 09:22:48

自旋转移扭矩磁阻随机存取存储器(

STT-MRAM)是一种持久性存储技术,可利用各种工业标准接口提供性能,持久性和耐用性。 Everspin推出了STT-MRAM产品,该产品利用称为JE-DDR4的JEDEC标准DDR4接口的变体,它包含了对完整系统支持所需的独特功能。本文将帮助工程师了解Xilinx FPGA控制器的Everspin STT-DDR4设计指南

2.启用ST-DDR4

为了使设计人员能够快速集成ST-DDR4支持,该过程从Xilinx Vivado开发环境中生成的现有8Gb DDR4 SDRAM-2666存储器接口生成器(MIG)开始。与8Gb DDR4 SDRAM的差异如下,并将在后续章节中进行说明:

1.时间安排(减少工作频率,增加行访问时间,增加计数器宽度并减小CAS页面大小)

2.加电(校准–校准期间启用了防乱涂模式)

3.掉电(将所有相关数据塞入或移动到持久性存储器阵列中)

4.性能(增加管道深度并提高数据传输效率)

注意:健壮的ST-DDR4持久性存储器设计还需要系统级的纠错码(ECC)方案,但该文档不在本文范围之内。

3. DDR4 SDRAM-1333内存接口

在Xilinx设计环境中,将根据代表8Gb

SDRAM DDR4-2666的速度和时序特性的输入参数生成DDR4接口逻辑。

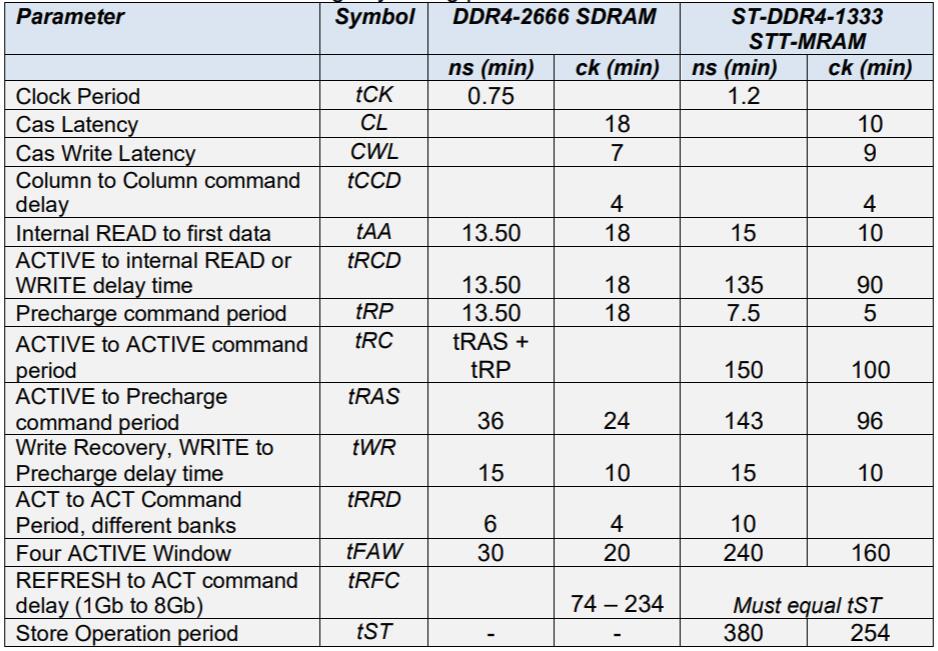

该表显示了DDR4和ST-DDR4的关键时序参数

由于MIG无法使用当前JEDEC标准以外的参数创建接口逻辑,因此必须首先创建兼容JEDEC的DDR4控制器。

everspin 1Gb ST-DDR4 1333器件最类似于8Gb DDR4-2666 SDRAM器件,因此请使用8Gb DDR4 SDRAM 2666规格SDRAM DDR4-2666中的时序值,一旦创建了DDR4接口逻辑,就可以修改时序,上电,掉电和性能参数,以启用ST-DDR4持久性存储器。

强烈建议在创建MIG之后,在Vivado中创建一个示例测试台,方法是右键单击.xci文件并选择名为“ Open IP Example Design ...”的菜单项。创建示例设计将创建一个新的Vivado项目。以及模拟新创建的MIG所需的所有测试文件。请参见Xilinx MIG创建教程,使用Vivado MIG为UltraScale设计存储器接口和控制器,以及存储器接口设计中心-UltraScale DDR4/DDR4存储器。

本文关键词:everspin STT-DDR4

相关文章:everspin非易失性存储器MR4A16B

深圳市英尚微电子有限公司是一家专业的静态随机记忆体产品及方案提供商,十年来专业致力代理分销存储芯片IC, SRAM、MRAM、pSRAM、 FLASH芯片、SDRAM(DDR1/DDR2/DDR3)等,为客人提供性价比更高的产品及方案。

英尚微电子中国区指定的授权代理:VTI、NETSOL、JSC济州半导体(EMLSI)、Everspin 、IPSILOG、LYONTEK、ISSI、CYPRESS、ISOCOME、PARAGON、SINOCHIP、UNIIC; 著名半导体品牌的专业分销商 如:RAMTROM、ETRON、FUJITSU、LYONTEK、WILLSEMI。

更多资讯关注SRAMSUN. www.sramsun.com 0755-66658299